Interfacing 8155 I/O ports and 8279 with multiple Addresses

Last Updated :

03 Mar, 2020

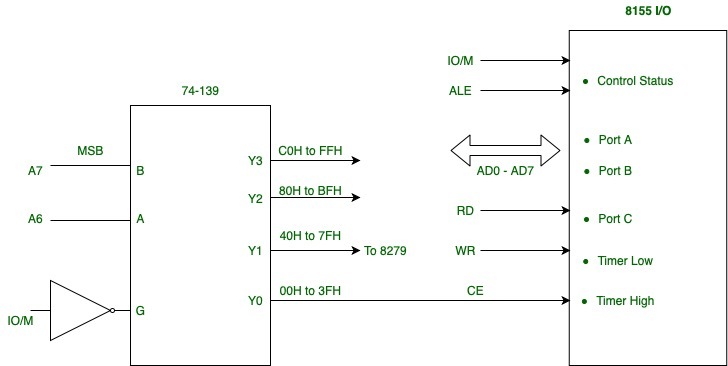

This article is about a decoding technique using the 74139, a 2-to-4 decoder.

The above mentioned device has two 2-to-4 decoders inside, one is used for interfacing I/O ports and the second is used for interfacing memory.

Let’s see I/O interfacing:

- The input to the decoder are the address lines A7 and A6.

- The decoder is enabled by the IO/M signal through an inverter.

- Whenever the processor asserts IO/M high to access an I/O port, the decoder becomes active.

- The address lines A5-A0 are not decoded in this schematic, some of them are connected to programmable I/O devices such as the 8155 and 8279

The figure will look something like this:

Figure – Interfacing 8155 I/O ports and 8279

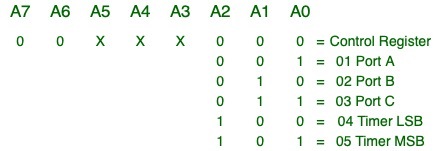

8155 I/O Addresses:

Figure – 8155 I/O Addresses

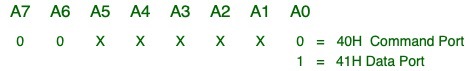

8279 I/O Addresses:

Figure – 8279 I/O Addresses

Multiple I/O Addresses:

The 8279 needs only two addresses, but because of the five don’t care lines, it occupies the space of 64 I/O addresses. In the case of the 8155, three addresses lines don’t care; therefore, it has eight sets of address ranges for its I/O ports and the timer.

Advantages:

- Save Costs

- Save Space

Like Article

Suggest improvement

Share your thoughts in the comments

Please Login to comment...